Presquile

Si-Qubits technology de-risking for large scale integration

Project manager

Cécilia Dupré, CEA

Overview

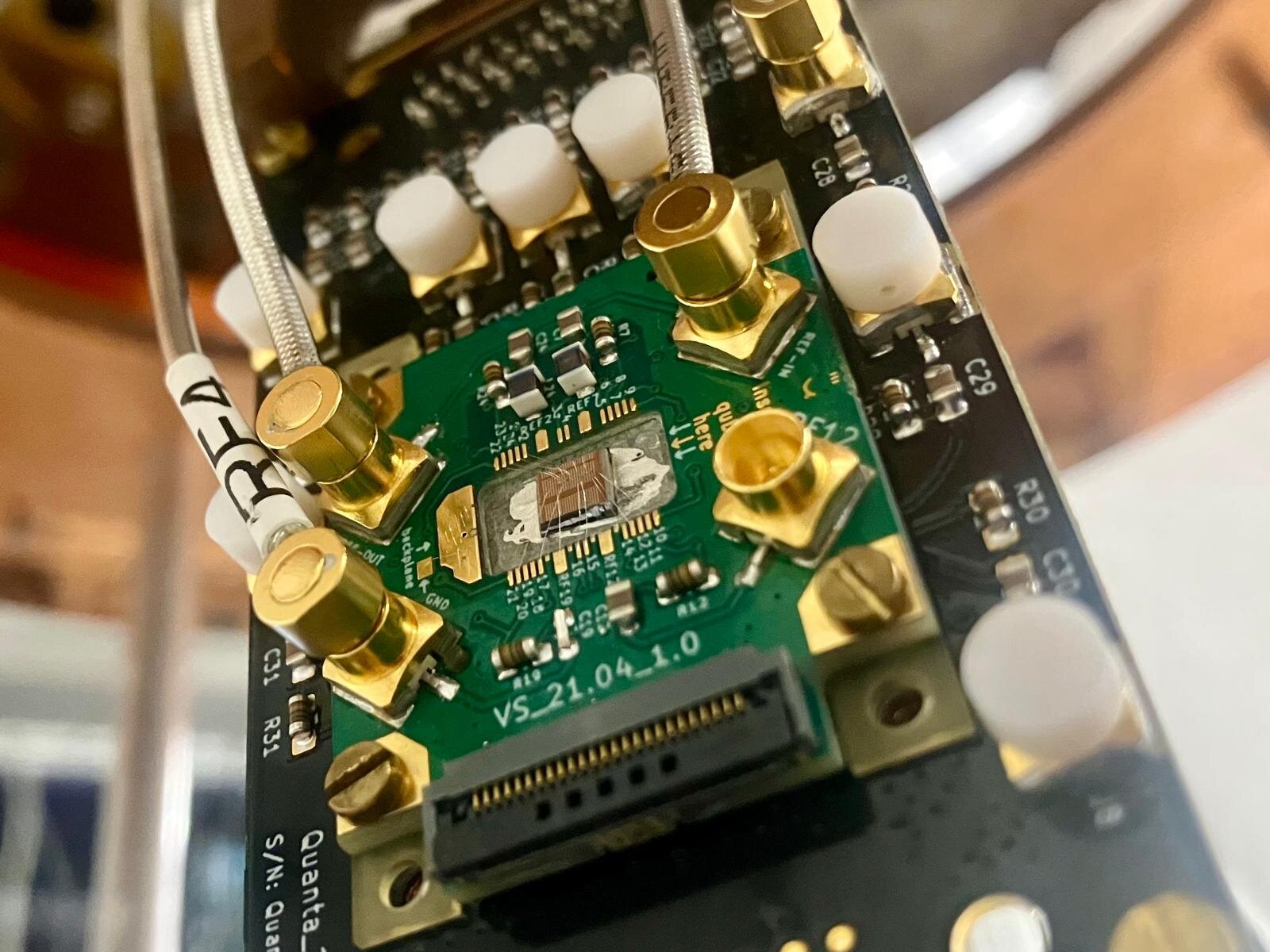

Silicon-based spin qubits have demonstrated their potential on an individual scale in several laboratories around the world. As early as 2016, PRESQUILE scientists demonstrated that industrial CMOS technology could be used to produce a qubit. The challenge now is to assemble and control a large number of these qubits.

Keywords: Spin qubits, spintronics, semiconductors

In a nutshell

The PRESQUILLE project is based on a two-track strategy:

- Study and demonstration of qubit variants (silicon qubits in a MOS structure, silicon Qubits in a SiGe/Si heterostructure, Ge Qubits in a SiGe/Ge heterostructure) which will enable statistical evaluations and can be integrated into the scalable architecture developed in parallel in VLSI technology.

- Study of two key elements to consolidate the dimensioning of large-scale architectures (spin/spintronics interfaces and variability).

During the first two years of the project, the first SiGe/Ge heterostructures were simulated, developed and characterized. They have demonstrated their potential for the realization of qubits through material studies, with the demonstration of a 1Qubit gate currently underway. The project involved the design and layout of various Si MOS quantum structures and CMOS cryogenic electronic circuits to demonstrate the control of several qubits.

The researchers developed magnetic memories which they were able to test up to 10K, and showed that magnetic writing could be achieved at low voltages. Co-integration of spintronic and quantum components on a 300 mm wafer scale is also underway. Finally, as part of the preparation of qubit arrays, they have demonstrated multiplexed spin reading on a 2×2 qubit array.

Challenges

- Identify and resolve the scientific and technological obstacles to integrating spin qubits via compatible CMOS technology.

- Evaluate alternative solutions to silicon in order to reduce clutter and/or relax technological constraints.

- Quantify the variability and performance of numerous silicon-based spin qubits.

- Exploit spintronics to open up options in qubit array architecture.

Tasks

- WP0: Management

- WP1: Explore the potential of SiGe-based heterostructures to improve qubit quality

- WP2: Develop spin/spintronics interfaces for efficient qubit addressing and control

- WP3: Measuring the variability and performance of spin qubits on silicon

- WP4: Simulation and modeling

Consortium

- CEA-Leti, Grenoble

- CEA IRIG, Grenoble

- Institut Néel (CNRS)