Presquile

Préparation des Si-Qubits pour l’Intégration à Large Echelle

Porteur

Cécilia Dupré, CEA

Aperçu

Les qubits de spin à base de silicium ont démontré leur potentiel à l’échelle individuelle dans plusieurs laboratoires dans le monde. Dès 2016, les scientifiques du projet PRESQUILE ont démontré que la technologie CMOS industrielle permettait de réaliser un qubit. L’enjeu consiste désormais à assembler et piloter un grand nombre de ces qubits.

Mots-clés : Qubits de spin, spintronique, semiconducteur

En résumé

Le projet PRESQUILLE propose une stratégie à deux voies :

- Étude et démonstration de variantes de qubits (qubits silicium dans une structure MOS, Qubits silicium dans une hétérostructure SiGe/Si, Qubits Ge dans une hétérostructures SiGe/Ge) qui permettront des évaluations statistiques et pourront être intégrées dans l’architecture scalable développée en parallèle en technologie VLSI

- Étude de deux éléments-clés pour consolider le dimensionnement des architectures à grande échelle (interfaces spin/spintronique et variabilité).

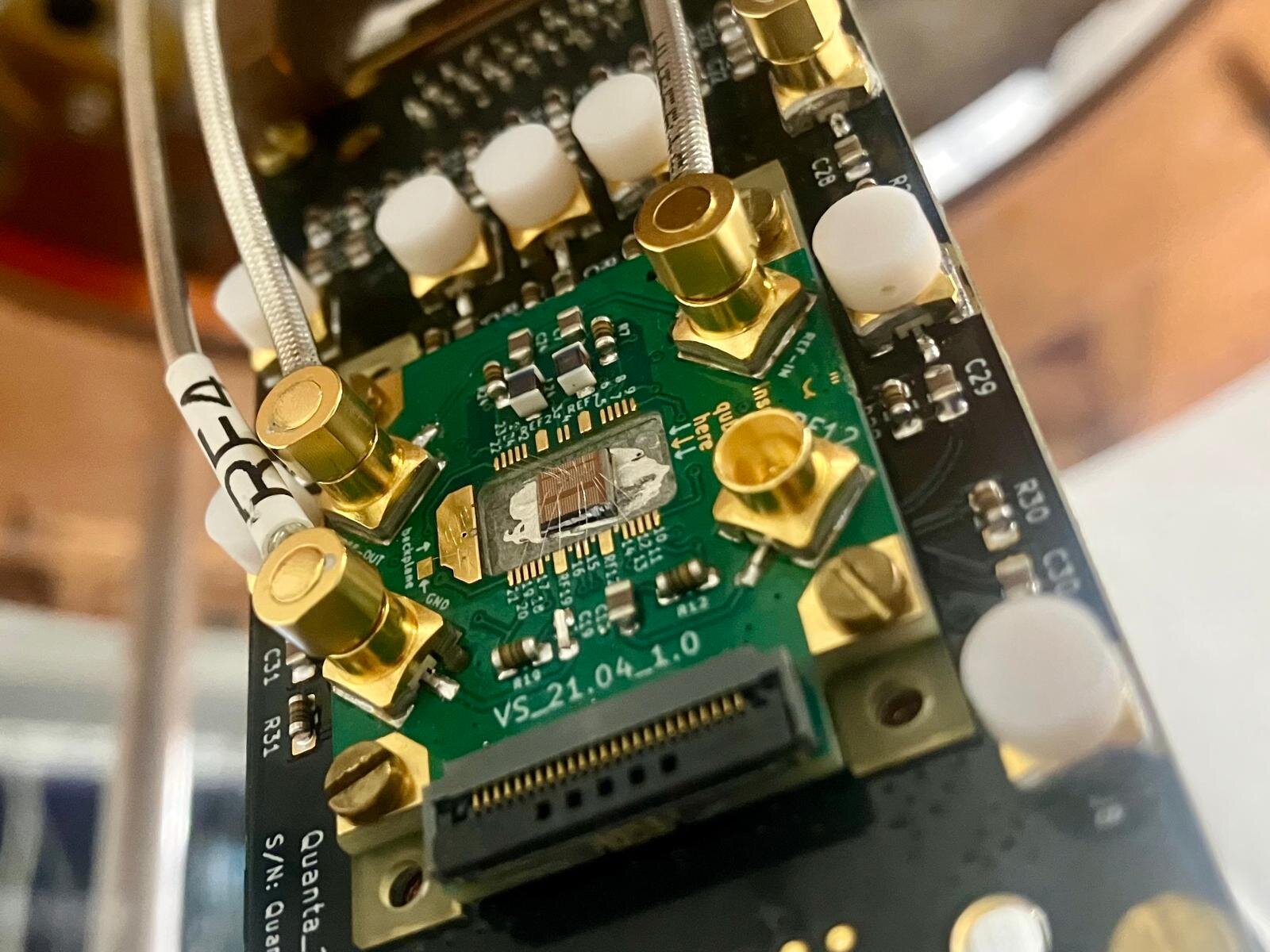

Sur les deux premières années du projet, les premières hétérostructures SiGe/Ge ont été simulées, développées et caractérisées. Elles ont montré leur potentiel pour la réalisation de qubits à travers des études matériaux, la démonstration d’une porte à 1Qubit étant en cours. Le projet a permis la réalisation du design et layout de différentes structures quantiques de type Si MOS et circuits électronique cryogénique CMOS pour montrer le contrôle de plusieurs qubits.

Les chercheurs et chercheuses ont développé des mémoires magnétiques qu’ils ont pu tester jusqu’à 10K et ont montré que l’écriture magnétique pouvait être réalisée à faible tension. La cointégration à l’échelle de wafer de 300 mm de composants spintroniques et quantique est par ailleurs en cours. Enfin, dans le cadre de la préparation de réseaux de qubits, ils ont montré la lecture multiplexée de spin sur un réseau 2×2 qubits.

Défis

- Identifier et résoudre les verrous scientifiques et technologiques pour l’intégration de qubits de spin via une technologie CMOS compatible.

- Évaluer des solutions alternatives au silicium afin de réduire le désordre et/ou relâcher les contraintes technologiques.

- Quantifier la variabilité et les performances des nombreux qubits de spin à base de silicium.

- Exploiter la spintronique pour ouvrir des options dans l’architecture des réseaux de qubits.

Tâches

- WP0 : Management

- WP1 : Explorer le potentiel des hétérostructures à base de SiGe pour améliorer la qualité des qubits

- WP2 : Développer des interfaces spin/spintronique pour l’adressage et le contrôle efficace des qubits

- WP 3 : Mesurer la variabilité et la performance des qubits de spin sur silicium

- WP4 : Actions de simulation et modélisation

Le consortium

- CEA-Leti, Grenoble

- CEA IRIG, Grenoble

- Institut Néel (CNRS)